May1625 - Advisor & Client: Dr. Randy Geiger

Sean Santella Hayle Olson David Ackerman Jaehyuk Han

04/27/16

### What is Latent Damage?

- → Is usually caused by an Electrostatic Discharge (ESD) event

- → Physically damages a device but is electrically undetectable

A device that has been *latently damaged* is still functional but may fail much sooner than expected.

### Does Latent Damage exist?

Some studies show that latent damage exists, while others don't

→ Latent damage is an on-going debate in the semiconductor industry

Study will examine bulk CMOS Commercial off-the-Shelf (COTS) devices

→ COTS devices typically have a Mean Time to Failure (MTTF) of 20 years

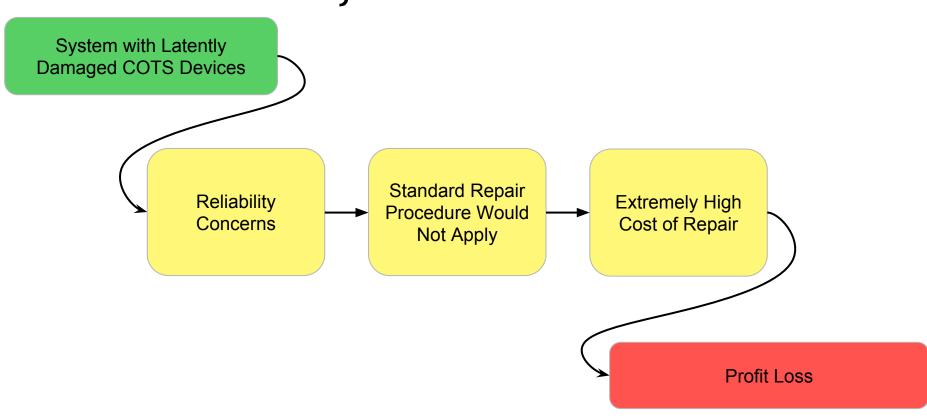

#### Why should we care?

### Hypothesis

If a non-catastrophic ESD event occurs on a semiconductor device, then latent damage exists.

This latent damage can cause the reliability of these devices to decrease.

Resulting in the MTTF to be shorter than the manufacturing specifications.

## **Overall Project Plan**

- → Destroy 50% of our devices

- Stress devices

- → Accelerate the lifetime of the "functional" devices

- Burn-in testing

- → Observe and analyze the MTTF

- Data analysis

#### An experiment with three parts:

#### ESD Stress

### ESD Stress

#### General Procedure

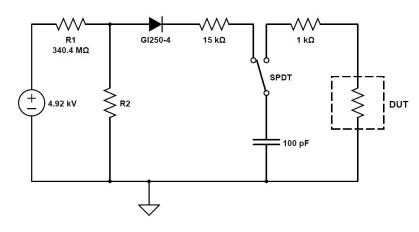

- → Devices will be exposed to an ESD event at a high-voltage level

- → Human Body Model (HBM)

- 100pF Capacitor charged to a high-voltage

- Discharged into Device Under-Test (DUT) with the output tied low

- → Texas Instruments (CD4049UBE)

- 6 CMOS inverters on one chip (hex inverter)

- → Determine a maximum stress level

# ESD Stress

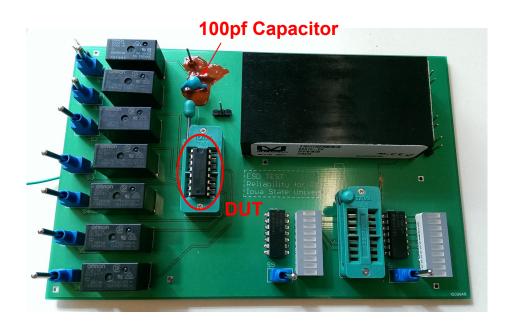

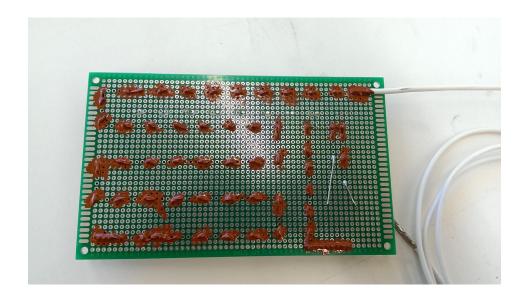

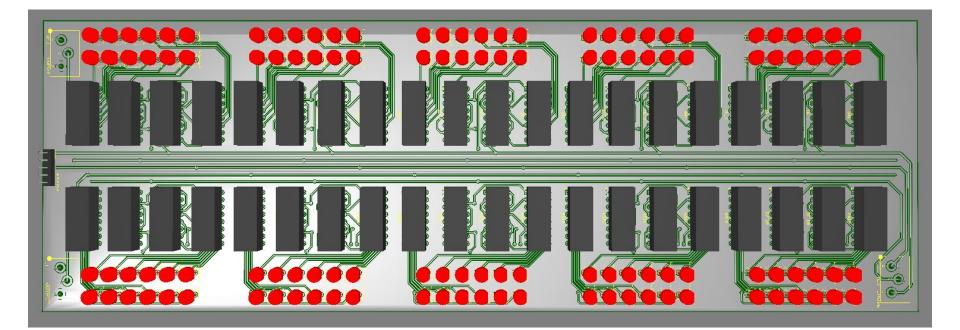

#### PCB

- → An ESD Stress PCB was previously created

- Simulate an ESD event

- Functionality check

- → Programmable high-voltage source was non-functional

- Re-purposed the PCB to use an agriculturally purposed highvoltage source

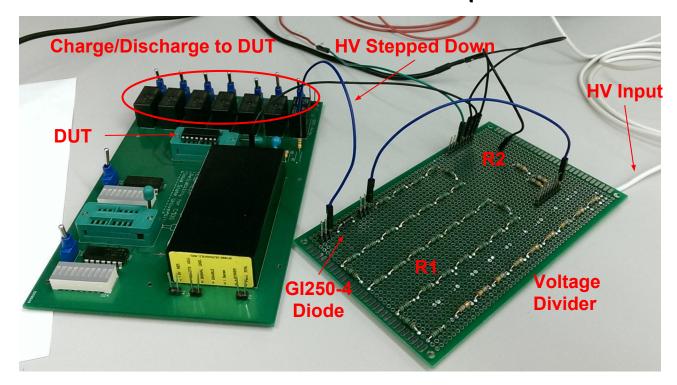

#### ESD Stress Setup

### ESD Stress

Challenges

- → High-voltage source has high frequency content

- High-speed diodes are required to minimize the effects

- Typically do not have large reverse breakdown voltages (V<sub>R</sub>)

- → A high V<sub>R</sub> is required to keep the capacitor charged during the negative cycle of the voltage source

- A diode with a V<sub>R</sub> of 4kV was used (Vishay SUPERECTIFIER GI250-4)

- → Oscilloscope can only handle roughly  $850V_{PP}$

- Designed and soldered an attenuator to check voltage on capacitor

- → The only way to verify that the ESD Stress setup is working is to catastrophically damage a device with a high-voltage discharge

- Components and devices used in the setup have to be soldered and insulated properly

#### Insulating Varnish

#### Stressing a Device

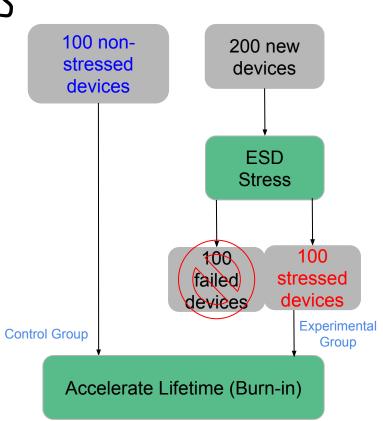

#### **Test Samples**

#### → Control Group

- 100 non-stressed devices

- 1 week of burn-in to acquire baseline data

- → Experimental Group

- 100 stressed devices

- 1 week of burn-in

#### Lifetime Acceleration

#### Burn-in

General Procedure

Once the parts are stressed, they are put into a burn-in oven.

The burn-in oven is used to accelerate the lifetime of the devices.

- → 112°C

- MTTF acceleration: 20 years to 1 week

- → DUTS are in a high-stress mode of operation

These parts will be checked regularly during the burn-in to determine if a failure has occurred.

## Burn-in

PCB

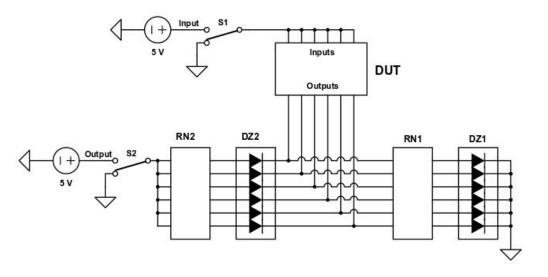

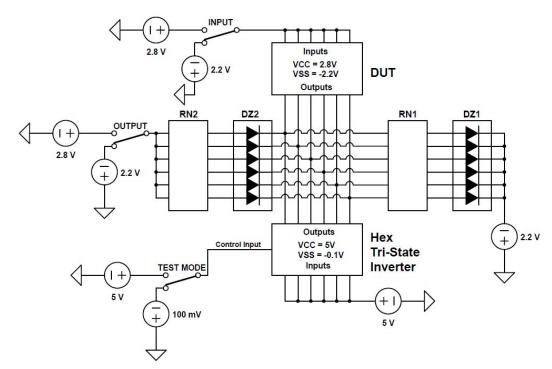

The PCB used to hold, test, and burn-in devices have two modes of operation:

- 1. Further stress devices while in burn-in, by holding the output of DUTs at their trip point.

- 2. Test the digital logic functionality of the devices, by disconnecting the output of the DUTs, to check when the devices failed.

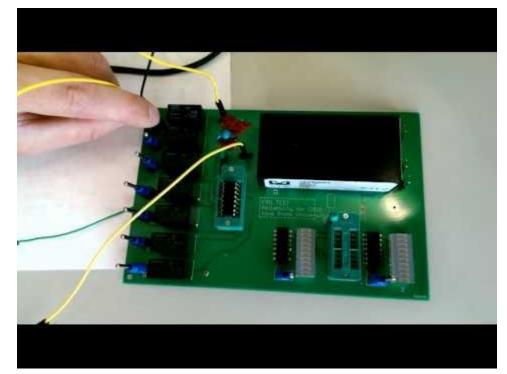

### Burn-in PCB

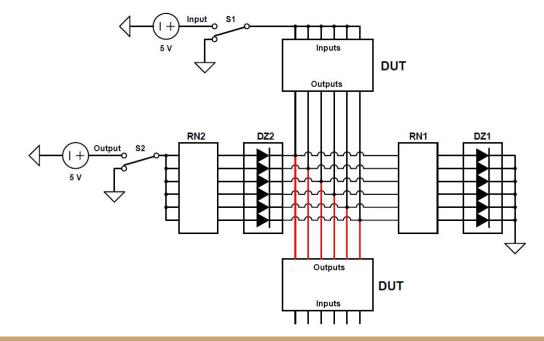

1st Design

12 Testing Clusters per PCB

1 Testing Cluster

### Burn-in PCB

1st Design

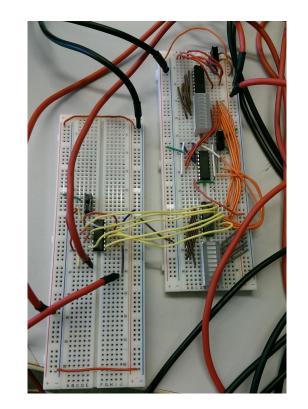

→ The bread board on the left is to test a single hexinverter

Latent Damage and Reliability in Semiconductor Devices

→ Circuit schematic:

### Burn-in PCB

Functionality Check

In the table below, 1 means "high" for the switch states, and 1 means conducting for the components.

| Sw      | itch     | Dio | des | Inverter Transistors |      |  |  |  |

|---------|----------|-----|-----|----------------------|------|--|--|--|

| "Input" | "Output" | DZ1 | DZ2 | PMOS                 | NMOS |  |  |  |

| 0       | 0        | 1   | 0   | 1                    | 0    |  |  |  |

| 0       | 1        | 1   | 0   | 1                    | 0    |  |  |  |

| 1       | 0        | 0   | 0   | 0                    | 1    |  |  |  |

| 1       | 1        | 0   | 1   | 0                    | 1    |  |  |  |

#### Burn-in PCB

Functionality Check

### Burn-in PCB

1st Design - Issues

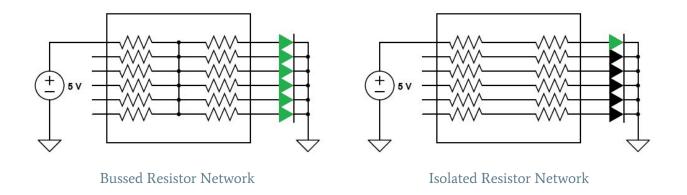

- 1. Resistor networks in the testing set-up are bussed instead of isolated.

- 2. All output gates of each testing setup are connected with other output gates

- These are design flaws that broke functionality of the old boards.

- We chose to make new boards to solve these issues.

#### Burn-in PCB

1st Design - Issues

1. Resistor networks in the testing set-up are bussed instead of isolated.

The LEDs are the visual indicators for collecting burn-in data; they need to work accurately

#### Burn-in PCB

1st Design - Issues

2. Output gates of each testing setup are connected with other output gates

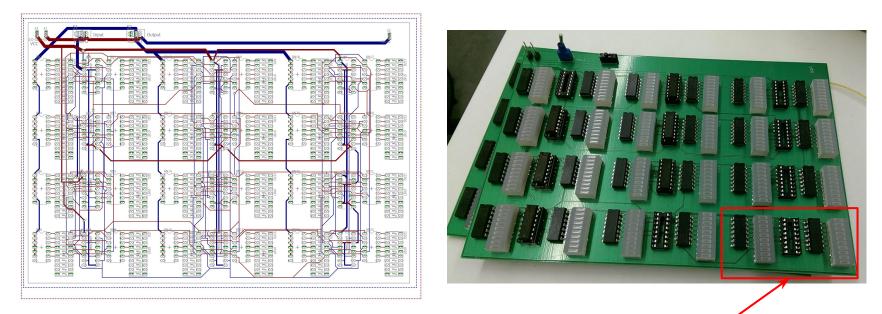

#### Burn-in PCB

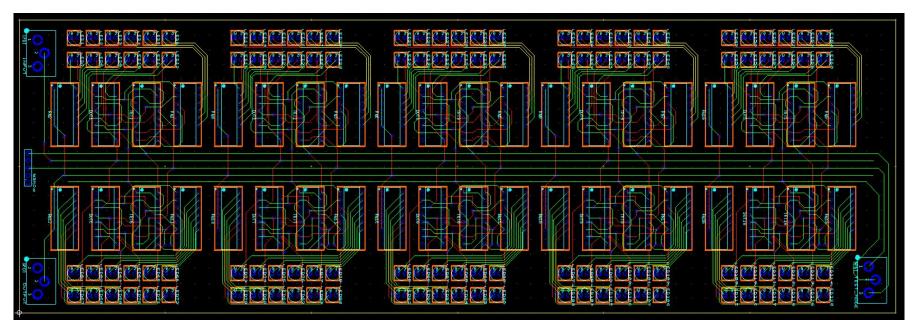

2nd Design

- → New circuitry to allow electronic switching of operation modes

- Output of DUT is either at the trip point or floating (disconnected) relative to the tri-states

# Burn-in PCB

2nd Design

- → Without the new circuitry, we would need 600 extra switches for the population.

- → Use of the tri-states only requires one extra switch per board, compared to the 1st design.

### Burn-in PCB

2nd Design

10 Testing Clusters per PCB

#### Burn-in PCB

2nd Design

### Burn-in PCB

2nd Design

- → Components need to withstand a temperature of 112°C

- → With the current design, these do not meet the specification:

- SPST Slide Switch [GF-123-0054]

- LED 3mm [OVLBR4C7]

- → The headers are okay because we can remove the plastic

| Component         | Temp  |

|-------------------|-------|

| PCB (FR-4)        | 140°C |

| Socket            | 125°C |

| Hex Buffer        | 125°C |

| Tri-St. Inverter  | 125°C |

| Resistor Array    | 125°C |

| Switch            | 104°C |

| LED 3mm           | 100°C |

| Headers (UL94V-0) | 90°C  |

# Reaching our Current Design

- $\rightarrow$  Determined issues with the 1st design of the burn-in PCB

- Resistor networks bussed

- DUT output gates connected

- → Solved the burn-in temperature with the HTOL model (112 $^{\circ}$ C)

- → Redesigned the burn-in PCB with electronic switching circuitry

- Hex tri-state inverters

- → Diagnosed some issues with the ESD stress PCB

- Insulating varnish to eliminate arcing

- → Considered our safety as a great concern

- Insulating varnish, properly insulated wires, soldering high-voltage circuits rather than breadboarding, etc.

#### Data Analysis

#### Data Analysis

**General Procedure**

After collecting the burn-in data for the experimental group, we can compare this to the control group data.

This will require statistical analysis, however our conclusion will only be accurate to a certain confidence level.

Our primary statistic of interest will be the *difference* in MTTF between the experimental and the control group.

#### Completed Work

- → Replaced the programmable high-voltage source

- → Determined issues and intended operation of existing PCB's

- → Breadboard implementation of 1st burn-in PCB design

- → Added second functionality to burn-in PCB

- High-stress mode

- → Calculated the burn-in temperature (112°C)

- → Created 2nd burn-in PCB design

- → Attempted to stress devices while troubleshooting high-voltage source

#### Future Considerations

- → Establish maximum stress level with ESD Stress System

- → Stress devices to create Experimental Group

- → Replace burn-in PCB components

- Must be rated at 112°C

- → Fabricate 10 burn-in PCBs and order components

- → Populate and solder burn-in PCB components

- → Accelerate lifetime of devices (burn-in)

- Control Group

- Experimental Group

- → Record data during burn-in of individual failing inverters

- → Analyze data to either confirm or deny hypothesis

- Only to a certain degree of confidence

### Thank you!

Any Questions?

#### Project Milestones & Schedule

|      |                                | Start Date | End Date  | %<br>Complete       | Q3 2015        |                       | Q4 2015 |               | Q1 2016 |          | Q         | Q2 2016  |         | Q3 2016 |          |           |

|------|--------------------------------|------------|-----------|---------------------|----------------|-----------------------|---------|---------------|---------|----------|-----------|----------|---------|---------|----------|-----------|

|      | Task Name                      |            |           |                     | Interesting of | and the second second |         | Oct Nov       | Dec     | Jan F    | eb Mar    | Apr      | May     | Jun     | Jul      | Aug S     |

|      |                                |            |           |                     | \$             | ର୍ ଖ                  | 2       |               |         |          |           | 10       |         |         |          |           |

| 1    |                                | 00/04/45   | 0.000/4.0 |                     |                | _                     |         |               |         |          |           | 1        |         |         |          |           |

| 2    |                                | 08/24/15   | 04/29/16  |                     |                | _                     |         |               |         |          | 1         |          |         |         |          |           |

| 3    | - Fall 2015 Semester           | 08/24/15   | 09/01/15  | 50%                 |                | -                     |         | 2015 Semeste  |         |          |           |          |         |         |          |           |

| 4    | Project Assignments            | 08/24/15   | 09/01/15  | 100%                |                |                       | Proje   | ct Assignment | ts      |          |           |          |         |         |          |           |

| 5    | Research                       | 09/01/15   | 10/07/15  | 100%                |                |                       |         | Research      |         |          |           |          |         |         |          |           |

| 6    | Website                        | 09/16/15   | 09/30/15  | 100%                |                |                       |         | Website       |         |          |           |          |         |         |          |           |

| 7    | Project Plan V1                | 09/30/15   | 10/02/15  | 100%                |                |                       |         | Project Plan  | V1      |          |           |          |         |         |          |           |

| 8    | Order Parts                    | 10/07/15   | 10/19/15  | 100%                |                |                       |         | Order Pa      | arts    |          |           |          |         |         |          |           |

| 9    | Design Document V1             | 10/20/15   | 10/23/15  | 100%                |                |                       |         | Design I      | Docun   | nent ∨1  |           |          |         |         |          |           |

| 10   | Prepare Presentation           | 11/10/15   | 12/08/15  | 100%                |                |                       |         |               | Prep    | are Pres | entation  |          |         |         |          |           |

| 11   | Presentation of Implementation | 12/08/15   | 12/08/15  | 1 <mark>0</mark> 0% |                |                       |         |               | Pres    | entation | of Impler | nentatio | n       |         |          |           |

| 12   | - Spring 2016 Semester         |            |           |                     |                |                       |         |               |         |          |           |          |         |         |          |           |

| 13   | Design & Verify Test System    | 01/11/16   | 04/11/16  |                     |                |                       |         |               |         |          |           | De       | sign &  | Verify  | Test S   | ystem     |

| 14   | Burn-in PCB                    |            |           | 90%                 |                |                       |         |               |         |          |           |          |         |         |          |           |

| 15   | ESD Stress PCB                 |            |           | <mark>95%</mark>    |                |                       |         |               |         |          |           |          |         |         |          |           |

| 16   | Fabricate Burn-in PCB's        | 04/11/16   | 04/18/16  | 0%                  |                |                       |         |               |         |          |           | Fi       | abricat | e Buri  | n-in PC  | B's       |

| 17   | Populate Burn-in PCB's         | 04/18/16   | 04/25/16  | 0%                  |                |                       |         |               |         |          |           |          | Popula  | te Bu   | n-in P   | CB's      |

| 18   | Burn-in Devices for 1 week     | 04/25/16   | 05/02/16  | 0%                  |                |                       |         |               |         |          |           |          | Burn-   | in De   | vices fo | or 1 week |

| 19   | Data Analysis                  | 05/02/16   | 05/03/16  | 0%                  |                |                       |         |               |         |          |           |          | Data    | Analy   | sis      |           |

| 20 💌 | Verify Hypothesis              | 05/03/16   | 05/03/16  | 0%                  |                |                       |         |               |         |          |           | -        | Verify  | Hypo    | thesis   |           |

| .21  | Prepare Presentation           | 03/28/16   | 04/29/16  | 90%                 |                |                       |         |               |         |          |           |          | Prepa   | re Pre  | esentat  | tion      |

| 22   | Final Presentation             | 04/27/16   | 04/29/16  |                     |                |                       |         |               |         |          |           |          | Final F | rese    | ntation  |           |

Updated on April 5<sup>th</sup>, 2016

#### Resource/Cost Estimate

|           |    | Updated: April 12th 2016                     |                |                                      |           |                      |  |  |  |

|-----------|----|----------------------------------------------|----------------|--------------------------------------|-----------|----------------------|--|--|--|

| Item Qty. |    | Reference                                    | Cost           | Part Description                     | Supplier  | Supplier #           |  |  |  |

| 1         | 10 | Murata Cermic Disc<br>Capacitors 100pf       | ~              | DHRB34A101M2BB                       | Mouser    | 81-DHRB34A101M2BB    |  |  |  |

| 2         | 2  | 1st Design<br>ESD Stress PCB                 | 5              | Provided                             | -         | 5                    |  |  |  |

| 3         | 10 | 1st Design<br>Burn-in PCB                    | 5              | Provided                             | -         | 5                    |  |  |  |

| 4         | 1  | Electric Fencer<br>High-Voltage Source       | \$53.49        | 5kV 0.2J                             | Gallagher | M20                  |  |  |  |

| 5         | 1  | Digital Electric<br>Fence Tester             | \$36.37        | Tests up to 20kV<br>3 Digit Read Out | Zareba    | DEFT-Z               |  |  |  |

| 6         | 50 | 10M Resistors (.25W)                         | \$5.74         | RNV14FAL10M0                         | Digi-Key  | RNV14FAL10M0CT-ND    |  |  |  |

| 7         | 1  | MG Chemicals<br>Insulating Varnish           | <b>\$</b> 9.44 | Red GLPT<br>55ml Bottle              | Amazon    | 4228-55ML            |  |  |  |

| 8         | 10 | Texas Instruments<br>Tri-St. Inverters (Hex) | \$5.81         | CD74HC366E                           | Digi-Key  | 296-33070-5-ND       |  |  |  |

| 9         | 20 | Vishay<br>Diode 4kV 250mA                    | \$7.08         | GI250-4-E3/54                        | Digi-Key  | GI250-4-E3/54GICT-ND |  |  |  |

|           |    | TOTAL COST                                   | 5117.93        |                                      |           |                      |  |  |  |

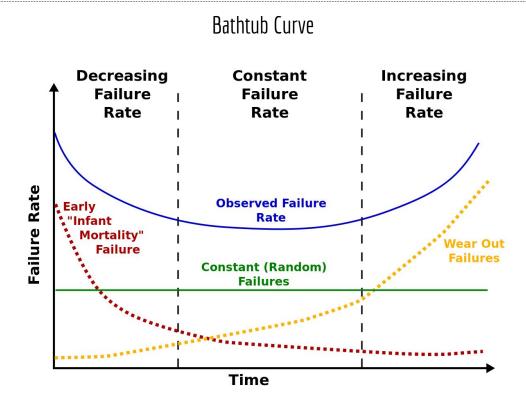

#### Semiconductor Reliability

Source: www.en.wikipedia.org/wiki/Bathtub\_curve

#### Burn-in

#### Calculations - HTOL Model

#### Variables:

A<sub>f</sub>: acceleration factor k: Boltzmann's Constant E<sub>a</sub>: activation energy (eV) T: temperature (Kelvin)

$MTTF_{hours} = 1/\lambda_{hours}$

D: number of devices tested (100 devices) H: test hours per device (168 hours = 1 week) EDH: equivalent device hours r: number of failures (50 fails)

#### Failures in Time (FIT) to Mean Time to Failure (MTTF):

FIT =  $λ_{FIT} = λ_{hours} \times 10^9$  (Failure rate (λ) per billion hours)

(Mean Time to Failure)

#### Burn-in

#### Calculations - HTOL Model

$MTTF_{years} = 20$  $MTTF_{hours} = 8760 \times MTTF_{vears} = 8760 \times (20)$  $\Rightarrow$  MTTF<sub>bours</sub> = 175,200  $\lambda_{\text{hours}} = 1/\text{MTTF}_{\text{hours}} = 1/(175,200)$  $\Rightarrow \lambda_{hours} = 5.708 \times 10^{-6}$  fails/hour EDH =  $r/\lambda_{hours}$  = (50 fails)/(5.708 × 10<sup>-6</sup> fails/hour) ⇒ EDH = 8,760,000 hours  $A_{f} = EDH/(D \times H) = (8,760,000 \text{ hours})/(100 \times 168 \text{ hours})$  $\Rightarrow$  A<sub>f</sub> = 521.43 Solve for T<sub>test</sub> to determine burn-in temperature:  $A_{f} = e^{\left[\left(\frac{E_{a}}{k}\right)\left(\frac{1}{T_{use}} - \frac{1}{T_{test}}\right)\right]} = 521.43 = e^{\left[\left(\frac{1.2eV}{8.617 * 10^{-5}\frac{eV}{K}}\right)\left(\frac{1}{328K} - \frac{1}{T_{test}}\right)\right]} \Rightarrow \mathsf{T}_{test} = \mathsf{384.69K} \approx \mathsf{112^{\circ}C}$

Source: www.microsemi.com